SMP

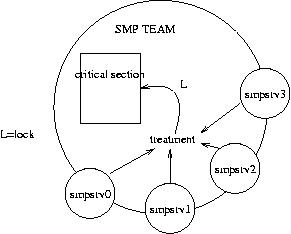

This section explains how SMP (Symetric Multi Processing) is implemented within LSE/OS.

Some SMP Specific terms

Here are some terms needed for understanding this document:

SMP Bootstrap

Just like the BSP, the AP's need to be boostraped. This section explains how:

The SMP program starts:

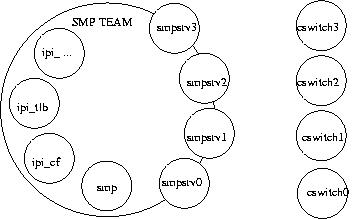

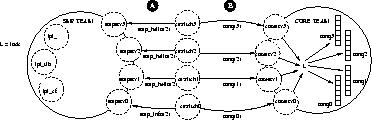

The SMP program installs IPI interrupts and SMP services for each processor. It also make AP's bootstraping to protected mode (see the smplo.S assembly file) and make them executing the smpkern task (they are in fact context switchers):

Once they are booted, AP's send a smp_hello() request to their corresponding services. They call then runq() for determining the next task to execute:

Services and interrupts in SMP

There is one IDT (Interrupt Descriptor Table) per processor: this implies that drivers must be explicitely programmed to support the SMP mode.

E.g. the timer service has an entry point per cpu:

But it also has a tick interrupt per cpu:

Scheduling policy then could be done according to different ways:

For now, SMP was only tested with simple tasks (e.g. cnt) that use only coresrv services.

Spinlocking in SMP

Altough in monoprocessor mode, servicing guarantees non-interruptibility, in SMP mode, two processors could execute the same code twice. For avoiding this we need to spinlock critical sections. There are two ways for doing this:

Spinlock are disseminated into the code to protect critical sections:

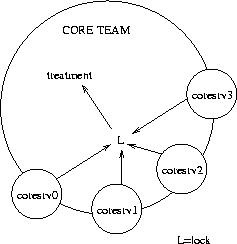

Spinlock are done at the door of the service, as in coresrv, for simplifying the code: